Skew |VLSI Concepts

Jan 20, 2016 · It's very important to understand the Skew and how it impact the timing analysis. Few different flavor of Definition. It's a difference between the clock arrival time across the chip.

Sep 27, 2018 · To minimize skew, balance clock paths using H-tree or matched-tree clock distribution structures. If possible, route data and clock in opposite directions; eliminates races at the cost of performance. The use of gated clocks to …

Types Of Clock Skew |VLSI Concepts - VLSI EXPERT

Different Type of Clock Skew. Positive Skew. Negative Skew, Pulse Skew, Internal and External Skew, Process Skew.

What is Skew in VLSI? - Maven Silicon

Mar 22, 2024 · Skew in VLSI, refers to the discrepancy or variation in signal arrival times among different paths within a chip. It represents the difference in propagation delay encountered by signals taking distinct routes from a common starting point to their respective destinations.

Clock Skew - VLSI Master

Skew is defined as the difference between the Arrival Time of the Clock Signal at the Clock pin of the Capture Flop and the Launch Flop. (Arrival Time at Capture Flop Pin – Arrival Time at Launch Flop Pin)

What is Skew in VLSI? - ChipEdge VLSI Training Company

Mar 15, 2024 · A skew in the VLSI design course occurs when a flip-flop is put near the clock source and another flip-flop is placed at the far end of the core region. In practice, the skew cannot be zero due to the disparity in connecting lengths.

Skew is the time delta between the actual and expected arrival time of a clock signal. Skew can be either extrinsic or intrinsic. The latter is internal to the driver (generator circuitry) and defined as the difference in propagation delays between the device outputs.

What is Clock Skew? Understanding Clock Skew in a Clock …

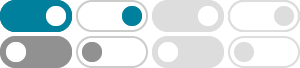

Oct 21, 2022 · Skew can be defined as positive if the receiving register receives the clock later than the transmitting register or negative in the opposite case. Clock skew becomes a serious problem in digital design as it can violate the timing constraints that the synchronous circuits rely on.

VLSI SoC Design: Clock Skew: Implication on Timing - Blogger

Mar 9, 2013 · Clock Skew: The difference in arrival times of the clock signal at any two flops which are interacting with one another is referred to as clock skew. Having said that, please note that skew only makes sense for two flops which are interacting with one another, i.e. they make a launch-capture pair.

VLSI Concepts: Target Skew - Blogger

Target Skew, the skew value on which the cts engine will try to build a balanced clock tree. In this post we will discuss about on which factors we will choose the target skew of our design & how’s that factors affect our design QOR.

- Some results have been removed