Low-voltage differential signaling - Wikipedia

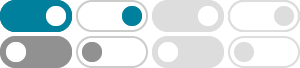

Low-voltage differential signaling (LVDS), also known as TIA/EIA-644, is a technical standard that specifies electrical characteristics of a differential, serial signaling standard. LVDS operates at low power and can run at very high speeds using inexpensive twisted-pair copper cables.

The LVDS standard for Low Voltage Differential Signaling is becoming the most popular differential data transmission standard in the industry. This is driven by two simple features of the bus, Gigabits @ milliwatts! It delivers the speed without consuming the power. In addition, it brings along a whole set of other benefits that

Low Voltage Differ- ential Signaling (LVDS) is a high speed (>155.5 Mbps), low power general purpose interface standard that solves the bottleneck problems while servicing a wide range of applica- tion areas. This application note explains the key advantages and ben- …

Bus LVDS (BLVDS) is a new family of bus interface circuits invented by National Semiconductor based on LVDS tech- nology. This family of interface devices is optimized for multi- point cable and backplane applications.

AN-1177: LVDS and M-LVDS Circuit Implementation Guide

Low voltage differential signaling (LVDS) is a standard for communicating at high speed in point-to-point applications. Multipoint LVDS (M-LVDS) is a similar standard for multi-point applications.

Implementing Bus LVDS Interface in Supported Intel® FPGA …

Bus LVDS (BLVDS) extends the capability of LVDS point-to-point communication to multipoint configuration. Multipoint BLVDS offers an efficient solution for multipoint backplane applications.

BLVDS takes care of most connections - EE Times

Sep 18, 2000 · Bus LVDS brings the advantages of point-to-point LVDS (very high speed, ultralow power, low noise and EMI, and low cost) to multipoint and multidrop architectures. BLVDS works over both cable and printed-circuit board (backplane) buses.

Bus LVDS addresses the issue of driving a low impedance interconnect by boosting its driver current to about 10mA. This means that into a load as low as 30Ω, a 300mV differential signal is maintained.

Implementing Bus LVDS Interface - EEWeb

Aug 14, 2012 · This application note describes how to implement the Bus LVDS (BLVDS) interface in the supported Altera® device families for high-performance multipoint applications. This application note also shows the performance analysis of a multipoint application with the Cyclone® III BLVDS example.

1.1.2.1. Implementing Bus LVDS I/O Interface

Intel devices offer on-chip Bus LVDS (BLVDS) I/O interface that you can use to implement the DisplayPort AUX channel. The BLVDS I/O is a bidirectional differential I/O interface and requires special pin assignment consideration.