Carry-lookahead adder - Wikipedia

A carry-lookahead adder (CLA) or fast adder is a type of electronics adder used in digital logic. A carry-lookahead adder improves speed by reducing the amount of time required to determine carry bits.

Carry Look-Ahead Adder - GeeksforGeeks

Feb 23, 2023 · A carry look-ahead adder reduces the propagation delay by introducing more complex hardware. In this design, the ripple carry design is suitably transformed such that the carry logic over fixed groups of bits of the adder is reduced to two-level logic.

Carry-Lookahead Adder: Explained for Beginners - Electronics Hub

May 21, 2024 · A carry-Lookahead adder is a fast parallel adder as it reduces the propagation delay by more complex hardware, hence it is costlier. In this design, the carry logic over fixed groups of bits of the adder is reduced to two-level logic, which is nothing but a transformation of the ripple carry design.

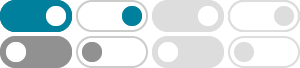

Types of carry generation logic (CGL): lookahead and ripple. With lookahead CGL adder above is a CLA. With ripple CGL adder above is equivalent to a ripple adder.

What is Carry Lookahead Adder : Block Diagram & Its Working

Dec 30, 2021 · What is Carry Lookahead Adder? This is a kind of electronics adder that is mainly employed in digital logic. A carry-lookahead adder is also called a fast adder that augments the speed required for determining carry bits.

Carry lookahead: group 16-bit adder using carry-lookahead with 4-bit adders (Fig. 4.24) Note that carry-in for each 4-bit adder is generated by carry-lookahead unit, not individual adders

Carry Look Ahead Adder - VLSI Verify

To tackle this issue, a carry look-ahead adder (CLA) can be used that reduces propagation delay with additional hardware complexity. CLA has introduced some functions like ‘carry generate (G)’ and ‘carry propagate (P)’ to boost the speed.

Carry Lookahead Adder in VHDL and Verilog with Full-Adders

A Carry Lookahead (Look Ahead) Adder is made of a number of full-adders cascaded together. It is used to add together two binary numbers using only simple logic gates . The figure below shows 4 full-adders connected together to produce a 4-bit carry lookahead adder.

The carry-lookahead is a fast adder designed to minimize the delay caused by carry propagation in basic adders. It utilizes the fact that, at each bit position in the addition, it can be determined if a carry with be generated at that bit, or if a carry will be propagated through that bit.

We can simplify the carry-MUX function into much more concise circuits with P&G signals using the recursive formula.