Xinlinx FPGA内的存储器BRAM全解 - CSDN博客

Apr 23, 2024 · 本文详细介绍了Xilinx7系列FPGA中BRAM的特点、分类(单端口、简单双端口、真双端口)、读写操作注意事项、三种写数据模式以及低功耗、最小面积和固定原语三种实现算法。 着重讨论了资源配置、读写冲突管理和优化策略。 Xilinx 7系列fpga中的 块RAM 存储高达 36 Kb 的数据,可以配置为 两个独立的18 Kb BRAM 或一个36 Kb RAM。 每个36Kb块RAM也可以配置成深度×宽度为64K × 1 (当与相邻的36KB块RAM级联时)、32K × 1、16K × 2、8K × 4、4K × 9 …

27 浅谈XILINX BRAM的基本使用 - 米联客(milianke) - 博客园

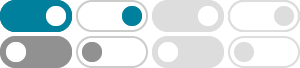

Dec 29, 2023 · Xlinx系列FPGA,包含两种RAM:Block RAM和分布式RAM(Distributed RAM),他们的区别在于,Block RAM是内嵌专用的RAM,而Distributed RAM需要消耗珍贵的逻辑资源组成。 前者具有更高的时序性能,而后者由于分布在不通的位置,延迟较大。 单口ROM,就是数据只读的,需要在IP初始化的时候,对ROM进行初始化,而且只有一个读接口。 端口A和端口B可以同时访问ROM. A端口写,B端口读. A 端口和B端口都可以读或者写. 支持3种模式,分别 …

FPGA设计中BRAM(Block RAMs)资源的使用(综合为BRAM) …

Oct 8, 2022 · RAM分为BRAM(Block RAMs)和 DRAM (Distributed RAM),即块RAM与分布式RAM,这两个差别在于BRAM是FPGA上固有的一些存储资源(针对不同型号的FPGA,其存储资源大小会有差别),而DRAM则是由LUT组合而成的。 所以在数据量较大的情况下,一般使用BRAM,尽量避免使用DRAM,导致LUT资源的浪费。 以Vivado平台为例,如果不指定综合为BRAM还是DRAM,则Vivado会根据RAM的大小自动判断综合为BRAM还是DRAM。 参考 博 …

Bram Meulblok - Manager Technical Solutions - LinkedIn

New digital one-step-CAD-to-Optic Manufacturing Process for Design, Prototyping, Sampling and Manufacturing of LED lighting optics and textures. ‘I have worked with Bram close to 3 years now,...

- Title: Manager Technical Solutions - …

- Location: Heliospectra Smart LED Lighting

FPGA从入门到精通(8)-BRAM - 知乎 - 知乎专栏

Jan 19, 2021 · 这个算法选项主要用于决定BRAM的拼接的方式,一般在BRAM深度、宽度较大的时候起作用(准确来讲是1个18K BRAM或者1个36K BRAM无法满足BRAM所需存储大小的时候)。它有三个选项,1.Minimum Area(小面积)。

URAM和BRAM有什么区别 - CSDN博客

Nov 21, 2019 · 本文详细比较了FPGA中的BlockRAM (BRAM)与UltraRAM (URAM),从容量、时钟、初始值、工作模式、实例化方式、级联方式等方面进行了深入解析。 无论是7系列 FPGA 、UltraScale还是UltraScale Plus系列FPGA,都包含Block RAM(BRAM),但只有UltraScale Plus芯片有UltraRAM也就是我们所说的URAM。 BRAM和URAM都是重要的片上存储资源,但两者还是有些显著的区别。 容量. BRAM的容量为 36Kb,且可当作两个独立的18Kb BRAM使用。 …

BRAM资源不够用?不怕!这里有FPGA BRAM省资源小秘招!

今天分享一下BRAM资源使用优化策略,以Vivado的 Block Memory Generator为例 。 存储深度和宽度较小,且LUT资源或URAM有富裕,可以用“Distribute BRAM”或“URAM”来替代。 这里需要注意使用的FPGA芯片型号,是否带URAM资源。 input clk, input [7:0] data_in, . input [5:0] wr_addr, input wr_en, input [5:0] rd_addr, output reg [7:0] data_out. if (wr_en) . ram[wr_addr] <= data_in; . data_out <= ram[rd_addr]; .

【FPGA ZYNQ Ultrascale+ MPSOC教程】33.BRAM实现PS与PL交互

有时CPU需要与PL进行小批量的数据交换,可以通过BRAM模块,也就是Block RAM实现此要求。 本章通过 Zynq 的GP Master接口读写PL端的BRAM,实现与PL的交互。 在本实验中加入了自定义的FPGA程序,并利用AXI4总线进行配置,通知其何时读写BRAM。 以下为本实验原理图,CPU通过AXI BRAM Controller读取BRAM数据,CPU仅配置自定义的PL BRAM Controller的寄存器,不通过它读写数据。 FPGA工程师工作内容. 以下为FPGA工程师负责内容。 1. 硬件环境搭建. …

【IP分析】BRAM的实用功能 - KevinChase - 博客园

May 24, 2017 · 最早的时候发现读取bram的addr必须+4而不是+1。 主要就在是否勾选“Byte Write Enable”,即是否按字节来操作。 在BRAM Controller模式下,默认勾选,PortA和PortB都是32bit位宽的,按照字节就是4个byte,所以会有we[3:0]共4个we信号。

zynq中PS访问BRAM(一) - 腾讯云

Nov 4, 2019 · PS端对PL端进行小批量的数据交换,可以通过BRAM模块,也就是Block RAM实现此要求。 通过Zynq的GP Master接口读写PL端的BRAM,实现与PL的交互。 PS端通过AXI BRAM Controller读取BRAM数据,CPU仅配置自定义的PL BRAM Controller的寄存器,不通过它读写数据。

Xilinx Vitis 2020.1修改工程占用的BRAM内存大小的方法

Dec 21, 2020 · 可以看到bram的大小已经生效了,变成了32kb。 这个时候要点一下Generate按钮,更新lscript.ld文件。 BRAM空间足够了,工程可以编译通过了:

bram · GitHub Topics · GitHub

Sep 20, 2020 · Flappy Bird core for MiSTer, MiST, DeMiSTify, Xilinx, GoWin, ... BRAM is a RAM resource certificate issued by Defibox. Add a description, image, and links to the bram topic page so that developers can more easily learn about it. To associate your repository with the bram topic, visit your repo's landing page and select "manage topics."

Meulbroek, Jonathan A._Meulbroek, Jonathan A.简介_Meulbroek, …

Meulbroek, Jonathan A.,现任职于Abbott Laboratories,曾任职于The University of Alabama at Birmingham、AbbVie等机构,个人H指数为19,累计发表论文27篇,论文总被引数累计2795次,主要研究方向涵盖医学、生物化学,遗传学和分子生物学、药理学,毒理学和药剂学、化学等领 …

Faculty & Staff – Financial Economics Institute

Professor Lisa Meulbroek is the Fritz B. Burns Professor of Finance at Claremont McKenna College, and specializes in executive compensation, risk management, and insider trading.

Meulbroek, L.K. (1992) An Empirical Analysis of Illegal Insider …

ABSTRACT: This paper wants to analyse the cyber-risk impact on economy in particular on the returns of the companies suffering information braches. The problem has become very …

ZYNQ PS及MicroBlaze访问FPGA端BRAM实战 - CSDN博客

Dec 3, 2020 · (1) Block RAM: Block RAM是PL部分的存储器阵列,为了与DRAM(分布式RAM)区分开,所以叫块RAM。 ZYNQ 的每一个BRAM 36KB,7020的BRAM有140个(4.9M),7030有265个(9.3M),7045有545个(19.2M)。 每一个BRAM都有两个共享数据的独立端口,当然是可以配置的,可用于片内数据缓存、FIFO缓冲。 (2) AXI BRAM Controller: PS和BRAM之间的事务由AXI BRAM Controller控制,可以是AXI总线形式,也可以是AXILite …

Michael Meulbroek's Lab - ResearchGate

Principal Investigator: Michael Meulbroek | ResearchGate, the professional network for scientists

Lisa K. Meulbroek - Claremont McKenna College

Lisa K. Meulbroek, Ph.D. "The Promise and Challenge of Integrated Risk Management." Risk Management and Insurance Review, 5 (4), 2002. "Company Stock in Pension Plans: How Costly Is It?" Harvard Business School Working Paper 02-058. "A Senior Manager’s Guide to Integrated Risk Management," Journal of Applied Corporate Finance, 14 (4), 2002, 56-70.

Xilinx FIFO Generator 需要注意BRAMs的资源消耗 - CSDN博客

Dec 29, 2020 · 本文将介绍一种利用手写fifo代替bram的fpga资源优化策略。上述代码实现了一个深度为16的fifo,数据宽度为8位。通过手写fifo代替bram,可以节省大量的资源,提高系统的性能。通过手写fifo代替bram,可以有效地节省fpga资源,提高系统性能。

A Senior Manager'S Guide To Integrated Risk Management

The author discusses the integrated risk management framework, emphasizing that a company can implement its risk management objectives in three fundamental ways: modifying its operations, using targeted financial instruments, or adjusting its capital structure.

- Some results have been removed